TMS320C6657CZHA IC DSP FIX/FLOAT POINT 625FCBGA

製品パラメータ

説明

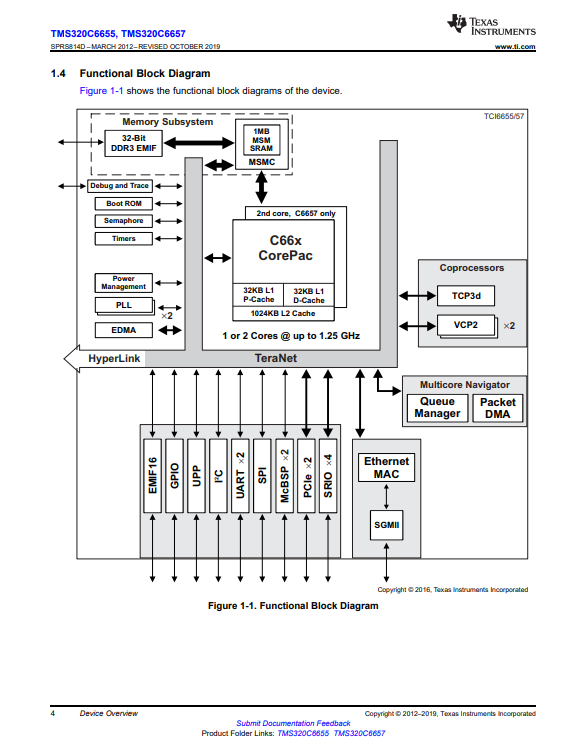

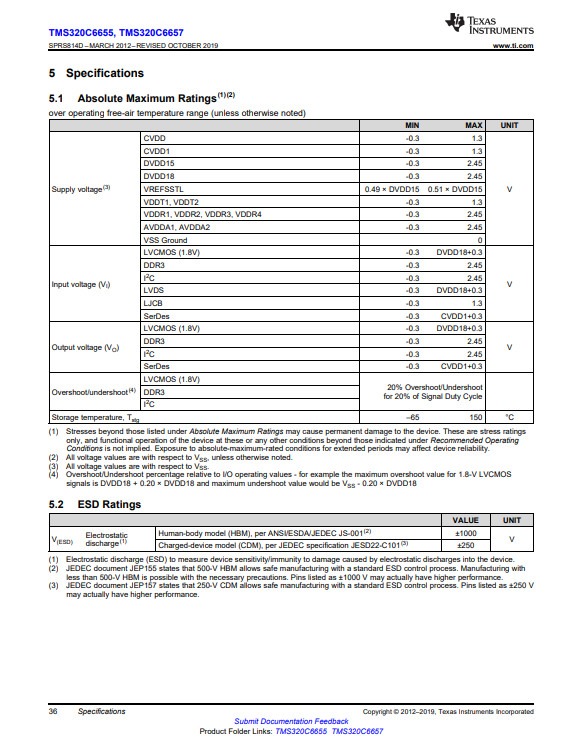

TI の KeyStone アーキテクチャは、さまざまなサブシステム (C66x コア、メモリ サブシステム、ペリフェラル、およびアクセラレータ) を統合するプログラマブル プラットフォームを提供し、いくつかの革新的なコンポーネントと技術を使用してデバイス内およびデバイス間通信を最大化し、さまざまな DSP リソースが効率的かつシームレスに動作できるようにします。このアーキテクチャの中心にあるのは、さまざまなデバイス コンポーネント間の効率的なデータ管理を可能にする Multicore Navigator などの主要コンポーネントです。TeraNet は、高速で競合のない内部データ移動を可能にするノンブロッキング スイッチ ファブリックです。マルチコア共有メモリ コントローラにより、スイッチ ファブリックの容量を利用することなく、共有および外部メモリに直接アクセスできます。固定小数点を使用する場合、C66x コアは C64x+ コアの 4 倍の積和 (MAC) 機能を備えています。さらに、C66x コアは浮動小数点機能を統合し、コアあたりの生の計算性能は、業界をリードするコアあたり 40 GMACS およびコアあたり 20 GFLOPS (動作周波数 1.25 GHz) です。C66x コアは、1 サイクルあたり 8 つの単精度浮動小数点 MAC 演算を実行でき、倍精度および混合精度演算を実行でき、IEEE 754 に準拠しています。C66x コアには、浮動小数点およびベクトル演算指向の処理を対象とした (C64x+ コアと比較して) 90 個の新しい命令が組み込まれています。これらの機能強化により、信号処理、数学、および画像取得機能で使用される一般的な DSP カーネルのパフォーマンスが大幅に向上します。C66x コアは、TI の前世代の C6000 固定小数点および浮動小数点 DSP コアと下位コード互換性があるため、ソフトウェアの移植性が保証され、より高速なハードウェアに移行するアプリケーションのソフトウェア開発サイクルが短縮されます。C665x DSP には、大量のオンチップ メモリが統合されています。32KB の L1 プログラムおよびデータ キャッシュに加えて、1024KB の専用メモリをマップされた RAM またはキャッシュとして構成できます。このデバイスには、共有 L2 SRAM および/または共有 L3 SRAM として使用できる 1024KB のマルチコア共有メモリも統合されています。すべての L2 メモリには、エラー検出とエラー訂正が組み込まれています。外部メモリへの高速アクセスのために、このデバイスには 1333 MHz の速度で動作する 32 ビット DDR-3 外部メモリ インターフェイス (EMIF) が含まれており、ECC DRAM をサポートしています。

| 仕様: | |

| 属性 | 価値 |

| カテゴリー | 集積回路 (IC) |

| 組み込み - DSP (デジタル信号プロセッサ) | |

| 製造元 | テキサス・インスツルメンツ |

| シリーズ | TMS320C66x |

| パッケージ | トレイ |

| 部品ステータス | アクティブ |

| タイプ | 固定/浮動小数点 |

| インターフェース | DDR3、EBI/EMI、イーサネット、McBSP、PCIe、I²C、SPI、UART、UPP |

| クロックレート | 1GHz |

| 不揮発性メモリ | ROM (128kバイト) |

| オンチップ RAM | 2.06MB |

| 電圧 - I/O | 1.0V、1.5V、1.8V |

| 電圧 - コア | 1.00V |

| 動作温度 | -40℃~100℃(TC) |

| 取付タイプ | 表面実装 |

| パッケージ・ケース | 625-BFBGA、FCBGA |

| サプライヤー デバイス パッケージ | 625-FCBGA (21x21) |

| ベース製品番号 | TMS320 |

関連している製品

-

電話

-

Eメール

-

スカイプ

-

ワッツアップ

ワッツアップ