OMAPL138EZWTD4 IC MPU OMAP-L1X 456MHZ 361NFBGA

製品パラメータ

説明

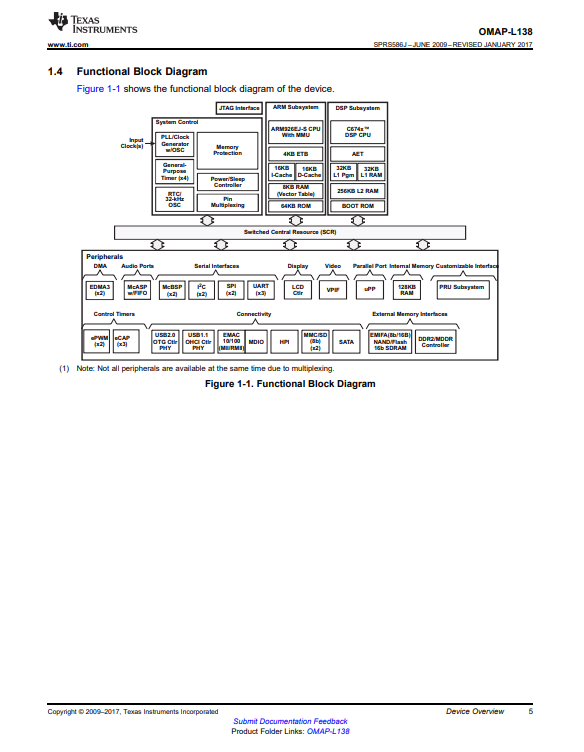

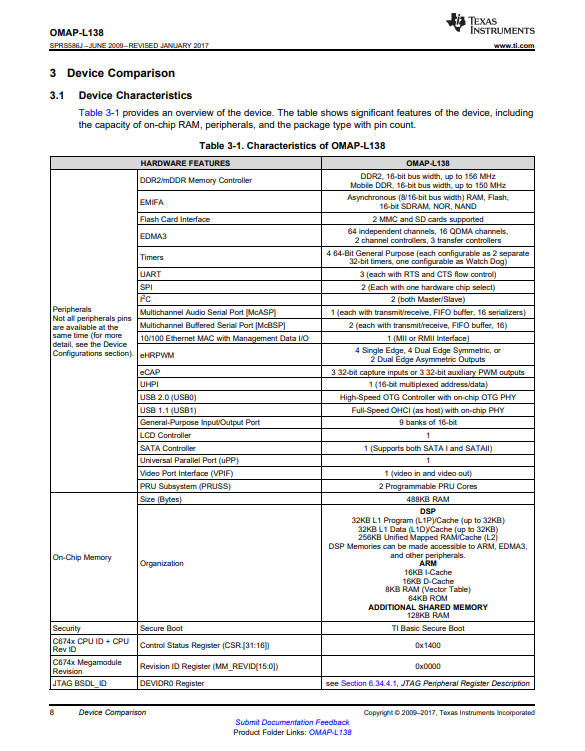

OMAP-L138 C6000 DSP+ARM プロセッサは、ARM926EJ-S と C674x DSP コアに基づく低電力アプリケーション プロセッサです。このプロセッサは、TMS320C6000™ プラットフォームの DSP の他のメンバーよりも大幅に低い電力を提供します。このデバイスにより、相手先商標製造会社 (OEM) および相手先商標製造会社 (ODM) は、完全に統合された混合プロセッサ ソリューションの最大限の柔軟性を通じて、堅牢なオペレーティング システム、豊富なユーザー インターフェイス、および高いプロセッサ パフォーマンスを備えたデバイスを迅速に市場に投入できます。このデバイスのデュアルコア アーキテクチャは、高性能 TMS320C674x DSP コアと ARM926EJ-S コアを組み込んだ、DSP と縮小命令セット コンピュータ (RISC) テクノロジの両方の利点を提供します。ARM926EJ-S は、32 ビットまたは 16 ビットの命令を実行し、32、16、または 8 ビットのデータを処理する 32 ビット RISC プロセッサ コアです。コアはパイプラインを使用して、プロセッサとメモリ システムのすべての部分が継続的に動作できるようにします。ARM9 コアには、コプロセッサ 15 (CP15)、保護モジュール、およびテーブル ルックアサイド バッファを備えたデータおよびプログラム メモリ管理ユニット (MMU) があります。ARM9 コアには、個別の 16 KB 命令キャッシュと 16 KB データ キャッシュがあります。どちらのキャッシュも、仮想インデックス仮想タグ (VIVT) との 4 ウェイ アソシエティブです。ARM9 コアには、8KB の RAM (ベクター テーブル) と 64KB の ROM もあります。デバイスの DSP コアは、2 レベルのキャッシュ ベースのアーキテクチャを使用します。レベル 1 プログラム キャッシュ (L1P) は 32 KB のダイレクト マップ キャッシュであり、レベル 1 データ キャッシュ (L1D) は 32 KB の 2 ウェイ セット アソシアティブ キャッシュです。レベル 2 プログラム キャッシュ (L2P) は、プログラムとデータ空間の間で共有される 256 KB のメモリ空間で構成されます。L2 メモリは、マップされたメモリ、キャッシュ、またはこの 2 つの組み合わせとして構成できます。DSP L2 は ARM9 およびシステム内の他のホストからアクセスできますが、DSP のパフォーマンスに影響を与えることなく、追加の 128KB の RAM 共有メモリを他のホストが使用できます。

| 仕様: | |

| 属性 | 価値 |

| カテゴリー | 集積回路 (IC) |

| 組み込み - マイクロプロセッサ | |

| 製造元 | テキサス・インスツルメンツ |

| シリーズ | OMAP-L1x |

| パッケージ | トレイ |

| 部品ステータス | アクティブ |

| コア プロセッサ | ARM926EJ-S |

| コア数/バス幅 | 1 コア、32 ビット |

| スピード | 456MHz |

| コプロセッサ/DSP | 信号処理;C674x、システム制御;CP15 |

| RAM コントローラ | SDRAM |

| グラフィックアクセラレーション | No |

| ディスプレイ & インターフェース コントローラ | 液晶 |

| イーサネット | 10/100Mbps (1) |

| SATA | SATA 3Gbps (1) |

| USB | USB 1.1 + PHY (1)、USB 2.0 + PHY (1) |

| 電圧 - I/O | 1.8V、3.3V |

| 動作温度 | -40℃~90℃(TJ) |

| セキュリティ機能 | ブート セキュリティ、暗号化 |

| パッケージ・ケース | 361-LFBGA |

| サプライヤー デバイス パッケージ | 361-NFBGA (16x16) |

| 追加のインターフェース | HPI、I²C、McASP、McBSP、MMC/SD、SPI、UART |

| ベース製品番号 | OMAPL138 |

関連している製品

-

電話

-

Eメール

-

スカイプ

-

ワッツアップ

ワッツアップ