EP1C6Q240C8N IC FPGA 185 I/O 240QFP

製品パラメータ

説明

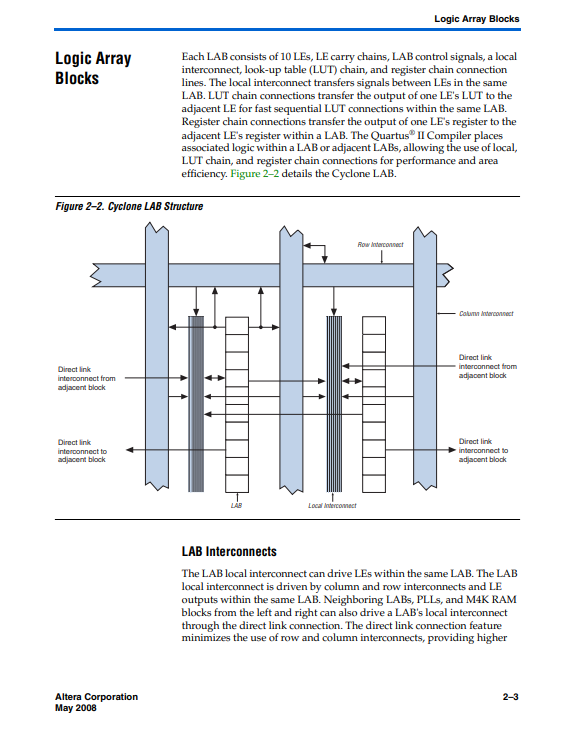

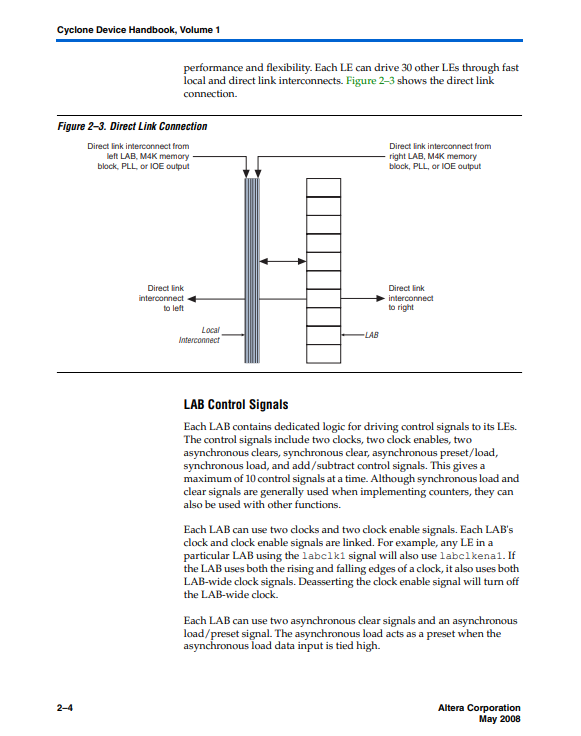

Cyclone® デバイスには、カスタム ロジックを実装するための 2 次元の行および列ベースのアーキテクチャが含まれています。さまざまな速度の列と行の相互接続は、LAB と組み込みメモリ ブロック間の信号相互接続を提供します。ロジック アレイは LAB で構成され、各 LAB には 10 個の LE があります。LE は、ユーザー ロジック機能の効率的な実装を提供するロジックの小さな単位です。LAB は、デバイス全体で行と列にグループ化されます。Cyclone デバイスの範囲は 2,910 ~ 20,060 LE です。M4K RAM ブロックは、4K ビットのメモリとパリティ (4,608 ビット) を備えた真のデュアル ポート メモリ ブロックです。これらのブロックは、最大 250 MHz で最大 36 ビット幅の専用のトゥルー デュアル ポート、シンプル デュアル ポート、またはシングル ポート メモリを提供します。これらのブロックは、特定の LAB 間のデバイス全体で列にグループ化されます。Cyclone デバイスは、60 ~ 288 K ビットの組み込み RAM を提供します。Cyclone デバイスの各 I/O ピンは、デバイス周辺の LAB の行と列の端にある I/O エレメント (IOE) から給電されます。I/O ピンは、66 および 33 MHz、64 および 32 ビット PCI 規格、最大 640 Mbps の LVDS I/O 規格など、さまざまなシングルエンドおよび差動 I/O 規格をサポートします。各 IOE には、双方向 I/O バッファと、入力、出力、および出力イネーブル信号を登録するための 3 つのレジスタが含まれています。デュアルパーパス DQS、DQ、および DM ピンと遅延チェーン (DDR 信号の位相を揃えるために使用) は、最大 133 MHz (266 Mbps) で DDR SDRAM や FCRAM デバイスなどの外部メモリ デバイスとのインターフェイス サポートを提供します。Cyclone デバイスは、グローバル クロック ネットワークと最大 2 つの PLL を提供します。グローバル クロック ネットワークは、デバイス全体を駆動する 8 つのグローバル クロック ラインで構成されます。グローバル クロック ネットワークは、IOE、LE、メモリ ブロックなど、デバイス内のすべてのリソースにクロックを提供できます。グローバル クロック ラインは、制御信号にも使用できます。Cyclone PLL は、クロック逓倍および位相シフトを備えた汎用クロッキングと、高速差動 I/O サポート用の外部出力を提供します。

| 仕様: | |

| 属性 | 価値 |

| カテゴリー | 集積回路 (IC) |

| 組み込み - FPGA (フィールド プログラマブル ゲート アレイ) | |

| 製造元 | インテル |

| シリーズ | サイクロン® |

| パッケージ | トレイ |

| 部品ステータス | 廃止 |

| LAB/CLB の数 | 598 |

| ロジックエレメント/セル数 | 5980 |

| 合計 RAM ビット | 92160 |

| I/O数 | 185 |

| 電圧 - 供給 | 1.425V~1.575V |

| 取付タイプ | 表面実装 |

| 動作温度 | 0℃~85℃(TJ) |

| パッケージ・ケース | 240-BFQFP |

| サプライヤー デバイス パッケージ | 240-PQFP (32x32) |

| ベース製品番号 | EP1C6 |

関連している製品

-

電話

-

Eメール

-

スカイプ

-

ワッツアップ

ワッツアップ