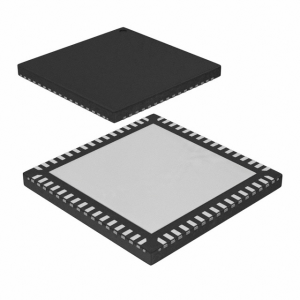

ATXMEGA256A3U-MH IC MCU 8/16BIT 256KB フラッシュ 64QFN

製品パラメータ

説明

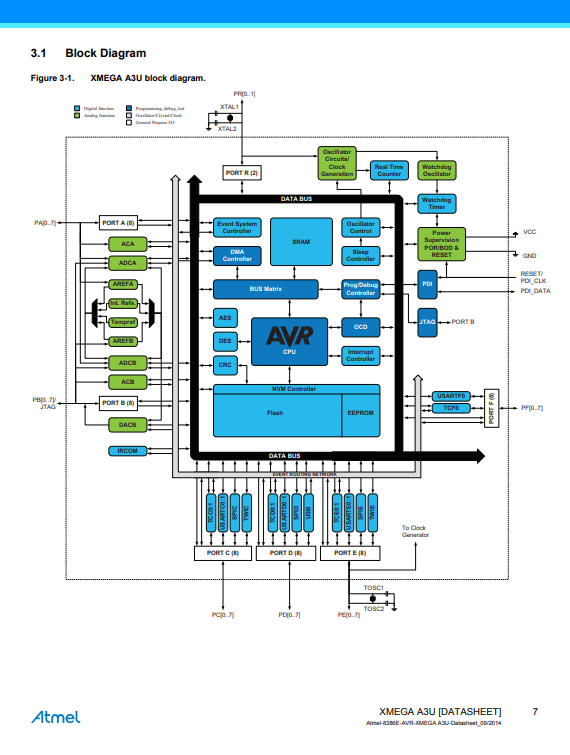

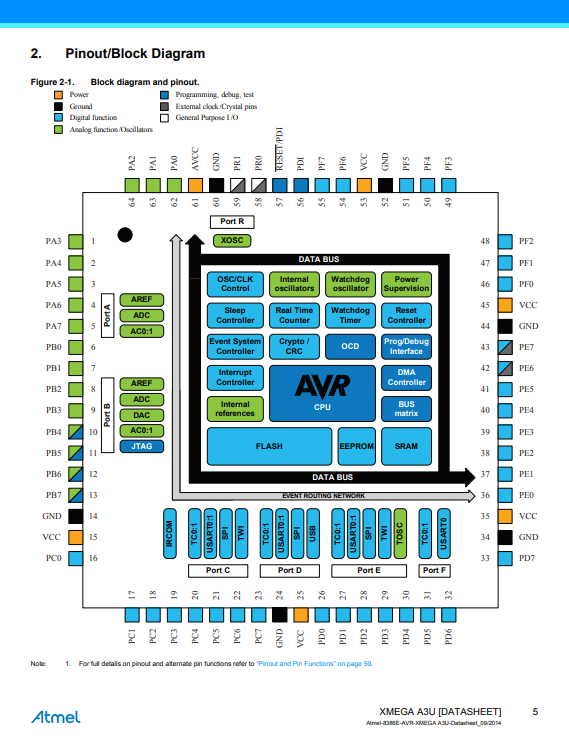

Atmel AVR XMEGA は、AVR 拡張 RISC アーキテクチャに基づく、低消費電力、高性能、および豊富なペリフェラル 8/16 ビット マイクロコントローラーのファミリーです。単一クロック サイクルで命令を実行することにより、AVR XMEGA デバイスは 1 メガヘルツあたり 1 秒あたり 100 万命令 (MIPS) に近い CPU スループットを達成し、システム設計者は処理速度に対する消費電力を最適化できます。AVR CPU は豊富な命令セットと 32 個の汎用ワーキング レジスタを組み合わせています。32 個のレジスタはすべて算術論理演算ユニット (ALU) に直接接続されているため、1 つのクロック サイクルで実行される 1 つの命令で 2 つの独立したレジスタにアクセスできます。結果として得られるアーキテクチャは、従来の単一アキュムレータまたは CISC ベースのマイクロコントローラよりも何倍も高速なスループットを達成しながら、コード効率が向上します。AVR XMEGA A3U デバイスは以下の機能を提供します。内部 EEPROM および SRAM;4 チャネル DMA コントローラ、8 チャネル イベント システムおよびプログラマブル マルチレベル割り込みコントローラ、50 本の汎用 I/O ライン、16 ビット リアルタイム カウンタ (RTC)。コンペアおよび PWM チャネルを備えた 7 つの柔軟な 16 ビット タイマー/カウンター。7つのUSART;2 つの 2 線式シリアル インターフェイス (TWI)。1 つのフルスピード USB 2.0 インターフェイス。3 つのシリアル ペリフェラル インターフェイス (SPI)。AES および DES 暗号化エンジン。プログラム可能なゲインを備えた 2 つの 16 チャネル、12 ビット ADC。1 つの 2 チャンネル 12 ビット DAC。ウィンドウモードを備えた4つのアナログコンパレータ(AC)。独立した内部発振器を備えたプログラマブル ウォッチドッグ タイマー。PLL とプリスケーラを備えた正確な内部発振器。プログラム可能な電圧低下検出。プログラミングとデバッグ用の高速な 2 ピン インターフェイスであるプログラム アンド デバッグ インターフェイス (PDI) が利用可能です。デバイスには、IEEE std もあります。1149.1 準拠の JTAG インターフェイスであり、バウンダリ スキャン、オンチップ デバッグ、およびプログラミングにも使用できます。

| 仕様: | |

| 属性 | 価値 |

| カテゴリー | 集積回路 (IC) |

| 組み込み - マイクロコントローラ | |

| 製造元 | マイクロチップ技術 |

| シリーズ | AVR® XMEGA® A3U |

| パッケージ | トレイ |

| 部品ステータス | アクティブ |

| コア プロセッサ | AVR |

| コアサイズ | 8/16 ビット |

| スピード | 32MHz |

| コネクティビティ | I²C、IrDA、SPI、UART/USART、USB |

| 周辺機器 | ブラウンアウト検出/リセット、DMA、POR、PWM、WDT |

| I/O数 | 50 |

| プログラムメモリサイズ | 256KB(128K×16) |

| プログラムメモリタイプ | 閃光 |

| EEPROM サイズ | 4K×8 |

| RAM サイズ | 16K×8 |

| 電圧 - 供給 (Vcc/Vdd) | 1.6V~3.6V |

| データコンバーター | A/D 16x12b;D/A 2x12b |

| 発振器の種類 | 内部 |

| 動作温度 | -40℃~85℃(TA) |

| 取付タイプ | 表面実装 |

| パッケージ・ケース | 64-VFQFN 露出パッド |

| サプライヤー デバイス パッケージ | 64-QFN (9x9) |

| ベース製品番号 | ATXMEGA256 |

関連している製品

-

電話

-

Eメール

-

スカイプ

-

ワッツアップ

ワッツアップ